## И ГОСУДАРСТВЕННЫЙ НАУЧНЫЙ ЦЕНТР РОССИЙСКОЙ ФЕДЕРАЦИИ В ИНСТИТУТ ФИЗИКИ ВЫСОКИХ ЭНЕРГИЙ

ИФВЭ 2012–19 ОЭА

В.А. Сенько, М.М. Солдатов, В.И. Якимчук

# 96-канальный модуль МИСС преобразования «заряд-цифра» для калориметров физики высоких энергий

Направлено в ПТЭ

УДК 539.1.07

### Аннотация

Сенько В.А., Солдатов М.М., Якимчук В.И. 96-канальный модуль МИСС преобразования «заряд-цифра» для калориметров физики высоких энергий: Препринт ИФВЭ 2012-19. – Протвино, 2012.-13 с., 7 рис., библиогр.: 10.

Представлены описание и основные технические характеристики регистрирующей подсистемы — 96-канального модуля преобразования «заряд-цифра», предназначенного для построения многоканальных электронных систем регистрации в физике высоких энергий.

### **Abstract**

Sen'ko V.A., Soldatov M.M., Yakimchuk V.I. 96 channel module MISS conversion "charge-digital" for calorimeters of high energy physics: IHEP Preprint 2012–19. – Protvino, 2012. – p. 13, figs. 7, refs.: 10.

A description and the main technical characteristics of the subsystem – 96 channel module conversion "charge-digital", designed to build of electronic registration systems in high-energy physics.

© Государственный научный центр Российской Федерации Институт физики высоких энергий, 2012

Современные эксперименты в физике высоких энергий ориентированы на поиск редких событий и это обстоятельство обусловливает основное требование к регистрирующей электронике - обеспечение высокой производительности систем регистрации. Решение этой задачи достигается использованием наиболее возможно совершенных устройств для выработки запускающего (триггерного) сигнала, осуществляющих максимальное подавление фоновых событий, и уменьшением «мертвого времени» собственно регистрирующих приборов. Здесь понятие «мертвого времени» включает в себя суммарное время преобразования принятой от детектора информации и время вычитывания преобразованных данных в устройство внешней буферной памяти, и является по существу длительностью сигнала «ЗАНЯТО», формируемого регистрирующим прибором. Система МИСС [1], разработанная в ИФВЭ, обеспечивает считывание рассеянных данных из каркаса с электроникой при высокой скорости передачи. Для работы в составе электроники регистрации и сбора данных с экспериментальных установок ИФВЭ продолжительное время использовались преобразователи "заряд-цифра" (ЗАЦП) [2-5], однако развитие микроэлектроники предоставило возможность для разработки гораздо более совершенных приборов для физического эксперимента. В настоящей работе описана 96-канальная регистрирующая подсистема ЛЭ-71, предназначенная для построения быстродействующих систем регистрации информации от ФЭУ калориметров физики высоких энергий, выполненная в виде модуля системы МИСС.

96-канальный модуль ЗАЦП ЛЭ-71.

Основными задачами, при разработке модуля были:

- -обеспечение малого «мёртвого» времени;

- -высокие метрологические характеристики (линейность характеристики, динамический диапазон, стабильность);

- -максимальная плотность размещения;

- -малая мощность потребления и возможность использования стандартных номиналов питающих напряжений;

- -возможность приема положительных, отрицательных и дифференциальных сигналов с высокими скоростями нарастания и спада;

- -возможность работы с различными источниками сигналов (электронные усилители газовых калориметров, ФЭУ), т.е. возможность согласования входного сопротивления канала регистрации ЗАЦП с различными линиями передачи (коаксиальный кабель, скрученная пара и пр.);

- -помехоустойчивость;

- -ремонтопригодность.

Модуль ЛЭ-71 представляет собой 96-ти канальный прибор преобразования "заряд-цифра" с подавлением нулевой информации (вычитанием «пьедесталов» преобразования) и промежуточным хранением данных до передачи их в буферную память контроллера МИСС. Конструктивно ЛЭ-71 состоит из материнской платы (Мат.П) и 24 мезонинных плат (Мез.П) типа QDC4, устанавливаемых в 24 разъёма типа SIMM30, расположенных на Мат.П.

Мезонинная плата QDC4.

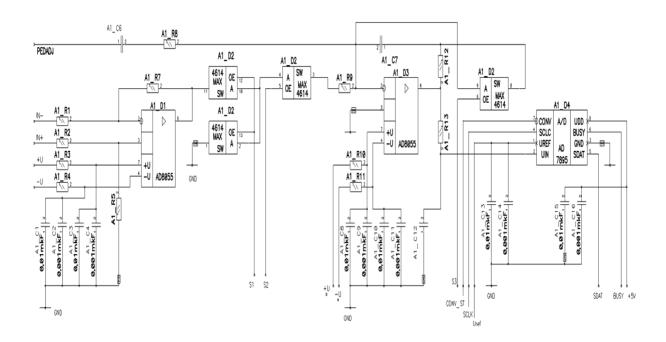

На печатной плате Мез.П смонтированы 4 канала преобразования заряда в цифру. Принципиальная схема одного канала преобразования показана на рис. 1. Схема включает в себя входной буферный усилитель с дифференциальным входом (микросхема D1 типа AD8055), параллельно-последовательное устройство линейного пропускания (часть микросхемы D2 типа MAX4616), управляемый интегратор (микросхема D1 и часть микросхемы D2) и аналого-цифровой преобразователь (АЦП, микросхема

D4). Использование микросхем операционных усилителей в буферном усилителе и интеграторе обеспечивает высокую помехоустойчивость к синфазным помехам в линии передачи от детектора, помехам и нестабильностям в цепях питания. АЦП – 12-разрядный преобразователь с временем преобразования 5 мксек и последовательным считыванием данных типа AD7895. Для управления схемой линейного пропускания и интегратором используется 3 строб-сигнала S1-S3, а для управления АЦП предназначены управляющие сигналы CONV\_ST и SCLK, которые являются общими для всех каналов модуля. SDAT — вывод данных — индивидуальный сигнал с каждого канала преобразования.

Рис. 1. Принципиальная схема одного канала преобразования.

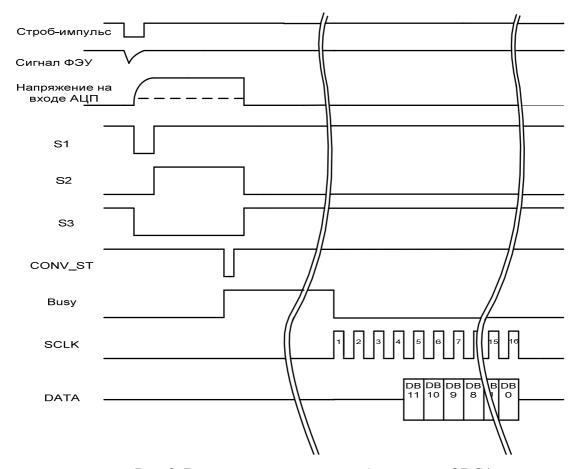

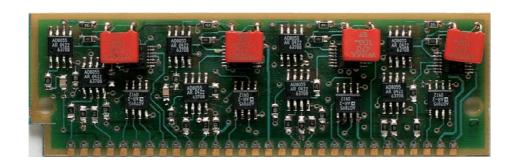

На рис. 2 приведены временные диаграммы работы канала QDC4, а на рис. 3 представлен внешний вид Мез.П.

Пунктирной линией на диаграмме «Напряжение на входе АЦП» обозначен уровень напряжения при отсутствии сигнала от ФЭУ – напряжение «пьедестала».

Рис. 2. Временные диаграммы работы канала QDC4.

Рис. 3. Внешний вид Мез.П.

Ниже приведены основные параметры канала преобразования платы QDC4:

• Интегральная нелинейность <0.05% при скорости нарастания входного сигнала  $\le 10$  мА/нсек и входном сопротивлении 50 Ом.

- Дифференциальная нелинейность ± 0,5 M3P, которая определяется примененной ИС АЦП типа AD7895 и может при необходимости быть улучшена применением ИС AD7894 (совместимый по выводам 14-разрядный вариант).

- Время преобразования-вычитывания

~6 мксек

• Стабильность.

Изменение величины «пьедестала» за сутки при изменении температуры окружающей среды на 15°C не превышает 0,3 МЗР.

- Динамический диапазон 12 бит.

- Полярность входных сигналов:

положительная;

отрицательная;

дифференциальные сигналы.

- Входное сопротивление канала QDC4- 1КОм.

- Диапазон длительностей строб-импульса

20-150 нсек.

Максимальный измеряемый заряд при Rвx=50 Ом

330 пКул (1000 пКул).

- Зависимость «пьедестала» от длительности строб-импульса и Rbx=50 Om  $\pm 0.2 \text{ пКул/нсек (тип.)}.$

- Скорость изменения входного сигнала при Rвх=50 Ом

10 мА/нсек.

- Количество каналов 4.

- Потребляемая мощность

$6B \times 15$  мА/канал,

-5В × 10 мА/канал.

• Размеры печатной платы QDC4  $90 \times 30 \text{ мм}^2$ .

Цифровая часть модуля ЛЭ-71.

Для достижения малого «мёртвого» времени цифровая часть модуля ЛЭ71 имеет следующие особенности:

- Запись (и последующее вычитывание) в выходную FIFO память только значащей информации.

- Аналого-цифровое преобразование и передача данных в устройства обработки происходит параллельно во всех 96 каналах за 5 мксек.

- Для обработки предназначено 3, параллельно работающих, устройства.

- Каждое из устройств функционирует в режиме конвейера (pipe-line), что сокращает время обработки до 50 нсек/канал (1,6 мксек/96 каналов).

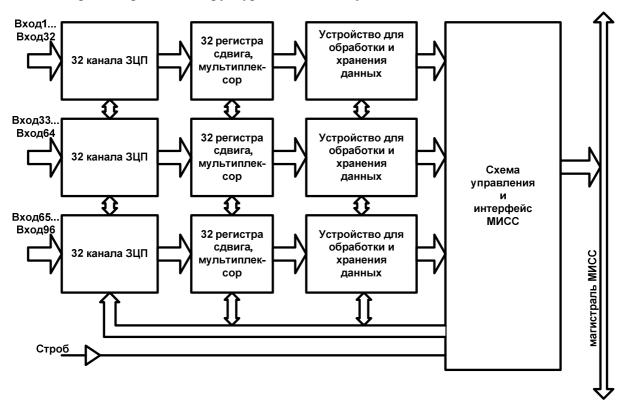

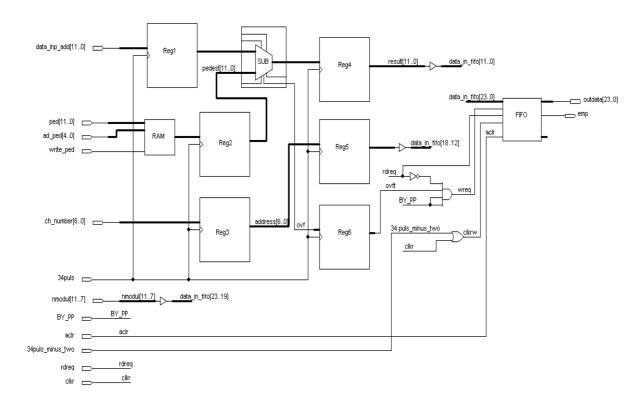

На рис. 4 приведена структурная схема модуля ЛЭ71.

Рис. 4. Структурная схема модуля ЛЭ71.

Модуль включает в себя 96 каналов ЗАЦП, 96 сдвиговых регистров – преобразователей последовательных кодов в параллельные, поступающих от АЦП АD7895 с мультиплексорами параллельных кодов, 3 устройства для обработки и промежуточного хранения данных для 32 каналов преобразования и схему управления с интерфейсом к магистрали МИСС. На коаксиальный разъем передней панели поступает сигнал Строб, длительность которого определяет время интегрирования входных сигналов,

поступающих на входные разъемы Вход1-Вход96 от детектора. При отсутствии сигнала Строб входные сигналы игнорируются. Данные из мезонинных плат с 96 каналов QDC4 передаются в 96 сдвиговых регистров одновременно в соответствии с последовательным протоколом примерно за 1,5 мксек и затем поступают в устройства для обработки и промежуточного хранения данных.

Схема управления и интерфейса к магистрали МИСС предназначена для управления временной селекцией сигналов, интегрированием, аналого-цифровым преобразованием, передачей данных из мезонинных плат QDC4, обработкой и занесением обработанных данных во внутреннюю буферную память модуля, а также реализации протоколов МИСС. Кроме того, она обеспечивает возможность записи в запоминающее устройство для "пьедесталов" и чтения его, запись и чтение данных в сдвиговые регистры для организации режима тестирования системы сбора, организацию тестовых режимов работы.

Последовательные коды, приходящие от ЗАЦП, преобразуются в параллельные на 96 12-разрядных регистрах сдвига и затем поступают в устройства обработки. Каждое из трёх устройств обработки обслуживает 32 канала регистрации. Для каждого события, отобранного триггерным устройством, количество каналов в калориметре, получивших сигнал, достигает 5–10%. Код, соответствующий отсутствию сигнала, но при наличии сигнала Строб, в канале регистрации индивидуален и обозначен как "пьедестал". Обработка информации состоит в вычитании из величин данных, получаемых от каналов преобразования, соответствующих "пьедесталов" и, если результат операции положителен, он заносится в устройство памяти типа FIFO вместе с соответствующим адресом – номером канала. В противном случае данные отбрасываются. Такой механизм обработки позволяет резко сократить объем передаваемой информации в магистраль МИСС, что приводит к уменьшению "мертвого времени" системы регистрации. Сокращению "мертвого времени" способствует также использование трех, работающих параллельно, устройств обработки данных и принцип конвейерной обработки, применённый в этих устройствах. Электрическая схема модуля практически полностью реализована в конфигурируемой микросхеме (FPGA ALTERA EP1K100QC208). Исключение составляют микросхемы для преобразования логических уровней.

На рис. 5 приведена схема одного из устройств обработки данных – часть проекта MAX+plus II [2]. Устройство содержит две группы регистров, а именно: Reg1 – 12 разрядов, Reg2 – 12 разрядов, Reg3 – 1 разряд, Reg4 – 12 разрядов, Reg5 – 12 разрядов, Reg6 – 1 разряд, а также запоминающее устройство RAM с произвольным доступом на 96 12-разрядных слов для хранения "пьедесталов", арифметическое устройство для вычитания "пьедесталов", запоминающее устройство FIFO типа first-in-first-out на 96 24-разрядных слов для промежуточного хранения данных и логические схемы для управления работой FIFO.

Рис. 5. Схема одного из 3 устройств обработки данных.

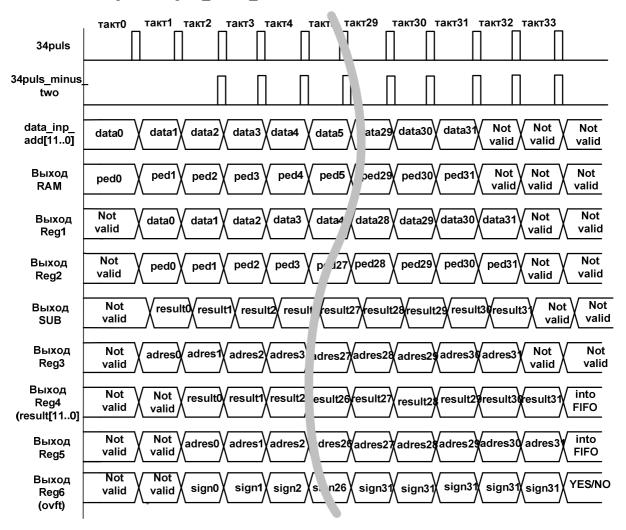

Наличие в устройстве обработки трёх каскадов для запоминания данных (две группы регистров и FIFO) позволяет организовать конвейерную обработку данных, которая существенно повышает производительность, и в конечном счете способствует уменьшению "мертвого времени". Временные диаграммы, поясняющие принцип работы устройства, приведены на рис. 6. Названия сигналов соответствуют названиям их в проекте MAX+plus II [6]. Входными сигналами схемы в режиме обработки

данных являются собственно данные, поступающие по 12-разрядной шине (data\_inp\_add[11..0]), номер обрабатываемого канала (7-разрядная шина ch\_number[6..0]) и номер модуля (5-разрядная шина nmodul[11..7]), синхронизирующие сигналы 34puls и 34puls\_minus\_two.

Рис. 6. Временные диаграммы, поясняющие принцип работы устройства обработки и промежуточного хранения данных.

Для полного цикла обработки данных с 32 каналов требуется 34 тактовых импульса (на рис. 5 сигнал 34puls). При записи в FIFO первые два отбрасываются (сигнал 34puls\_minus\_two). При дальнейшем протекании процесса обработки запись в FIFO происходит только в случае превышения величин данных над "пьедесталами", т.е. при высоком состоянии логического сигнала ovft. Скорость обработки данных устройством

составляет примерно 50 нсек/канал. Полное время обработки данных в модуле составляет 50 нсек  $\times$  32  $\sim$  1, 6 мксек. Для длительности строб-импульса равной 0,1 мксек, времени установления интегратора и выборки-хранения AD7895 Me3.П. QDC4 равном примерно 1 мксек, времени преобразования/считывания AD7895 равном 5 мксек, времени обработки -1,6 мксек и числе сработавших каналов около 10% количество принятых системой из 10 модулей ЛЭ71 (960 каналов регистрации) событий за 1 секундный сброс может достигать 50000.

В модуле предусмотрена развитая система диагностики, которая позволяет проверять работу всех узлов (памяти, вычитающего устройства и т.д.), качество монтажа и имитировать основной режим работы при отсутствии входных сигналов.

Конструкция и функции, выполняемые модулем, в режиме «адресных передач»[1].

Рис. 7. Внешний вид модулей ЛЭ-71.

Механическая конструкция представляет собой материнскую плату с установленными на ней 24 Мез.П. QDC4 посредством 24 разъемов SIMM-30. Материнская плата размещена в модуле МИСС двойной ширины.

Существует несколько вариантов исполнения модуля ЛЭ-71. Это:

- -вариант для регистрации дифференциальных сигналов от ионизационных детекторов с входными разъёмами под плоский кабель;

- варианты для регистрации однофазных сигналов (положительных или отрицательных ) от ФЭУ с различными типами входных разъёмов.

На рис. 7 приведен внешний вид модулей ЛЭ71. Потребляемая мощность примерно +6 B  $\times$  1,7 A и -5,2 B  $\times$  1,8 A.

Функции, исполняемые модулем в режиме адресных передач МИСС, следуюшие:

A(0)F(0)-чтение регистра INC, DA0-DA3;

A(0)F(3)-запись в регистр INC, DA0-DA3;

при этом:

если DA1=0 в модуле происходит обработка данных из входных сдвиговых регистров, полученных из QDC;

если DA1=1 в модуле происходит обработка данных из входных сдвиговых регистров, занесенных в модуль по функции A(2)F(3);

если DA2=0 обработка данных в модуле начинается по концу сигнала BUSY одного из 96 каналов преобразования;

если DA2=1 момент начала обработки данных в модуле определяется внутренней схемой системы обработки данных;

если DA3=0 будет производиться вычитывание данных из модуля в режиме синхронного ПЧИ;

если DA2=1 будет производиться вычитывание данных из модуля в режиме асинхронного ПЧИ;

A(1)F(0)-чтение регистра REG ADDRESS, DA1-DA7;

A(1)F(3)-запись в регистр REG ADDRESS, DA1-DA7;

A(2)F(0)-чтение входного преобразователя (сдвигового регистра) последовательного кода, DA1-DA12 (адрес канала заносится по A(1)F(3));

- A(2)F(3)-запись во входной преобразователь последовательного кода, DA1-DA12 (адрес канала заносится по A(1)F(3));

- A(3)F(0)-чтение RAM "пьедестала", DA1-DA12 (адрес канала заносится по A(1)F(3));

- A(3)F(3)- запись в RAM "пьедестала", DA1-DA12 (адрес канала заносится по A(1)F(3));

В настоящее время модули работают в составе различных экспериментальных установок ИФВЭ [7-10]. Общее количество используемых каналов ЗАЦП, построенных на основе модуля ЛЭ-71, около 10 тысяч.

.

## Список литературы

- [1] Бушнин Ю.Б., Ваньев В.С., Гончаров П.И. и др.- Препринт ИФВЭ 8847, Серпухов, 1988.

- [2] Бушнин Ю.Б., Денисенко А.А., Дунайцев А.Ф. М.М. Солдатов и др. Препринт ИФВЭ 79-37, Серпухов, 1979.

- [3] Бушнин Ю.Б., В.А. Сенько, М.М. Солдатов, В.И.Якимчук. Препринт ИФВЭ 86-31, Серпухов, 1979.

- [4] Бушнин Ю.Б., Зимин С.А., Сенько В.А., Солдатов М.М.- V Всесоюзный семинар по автоматизации исследований в ядерной физике и смежных областях. Ташкент, 15-17 ноября, 1988. Стр. 86.

- [5] Васильев М.В., Сенько В.А., Солдатов М.М.– Препринт ИФВЭ 99-49, Протвино 1999.

- [6] ALTERA Corporation, 1988-2002, MAX+plusII.

- [7] Боголюбский М.Ю., Викторов В.А., Петров В.С. и др.- Препринт ИФВЭ 2005-7, Протвино, 2005.

- [8] E.N. Ardashev, S.G. Basiladze, G.A. Bogdanova et al. 2007. 18 pp. Published in Instrum. Exp. Tech. 50 (2007) 646-663.

- [9] Recent results from VES experiment. 2009. VES Collaboration (V.Nikolaenko (Serpukhov, IHEP) et al.) 2011. 6 pp. Published in Int.J.Mod.Phys. A24 (2009) 295-303.

- [10] A data acquisition system of the FODS setup. A.A. Volkov, V.P. Efremov, A.Yu. Kalinin, et al. 2012. 8 pp. Published in Instrum. Exp. Tech. 55 (2012) 448-455, Prib. Tekh. Eksp. 4 (2012) 35-42.

Рукопись поступила 15 октября 2012 г.

| BA     | Сенько  | MM      | Солдатов, | ΒИ    | Якимчук |

|--------|---------|---------|-----------|-------|---------|

| D.4 X. | CCHBRO. | TAT TAT | Солдатов. | D.II. |         |

96-канальный модуль МИСС преобразования «заряд-цифра» для калориметров физики высоких энергий.

Препринт отпечатан с оригинала-макета, подготовленного авторами.

| Подписано в    | к печати 25.10.2012. | Формат    | $60 \times 84/16$ . | Цифровая печать. |  |  |

|----------------|----------------------|-----------|---------------------|------------------|--|--|

| Печ.л. 1.      | Уч.– изд.л.  1,25.   | Тираж 80. | Заказ 53.           | Индекс 3649.     |  |  |

| ACTY CHILLHADO |                      |           |                     |                  |  |  |

ФГБУ ГНЦ ИФВЭ 142281, Протвино Московской обл.

ПРЕПРИНТ 2012-19, ИФВЭ, 2012